Forum Index : Electronics : Various aspects of home brew inverters

Totem Pole Mosfet Driver For Mac Os

Totem Pole Mosfet Driver For Mac Free

Here Download free Samsung ML-2165W printer updates to enhance the performance of print, copy, scan, fax, USB, wi-fi, LAN, firmware drivers and utility driver for windows 7, 8, 10 operating system. It is possible that your Printer driver is not compatible with the newer version of Windows. Simply select the WPS WiFi Protected Set-up button on. MOSFET Driver, High Speed, Dual The MC34152/MC33152 are dual noninverting high speed drivers. And two high current totem pole. Fundamentals of MOSFET and IGBT Gate Driver Circuits 2.2 MOSFET Models There are numerous models available to illustrate how the MOSFET works, nevertheless finding the right representation might be difficult. Most of the MOSFET manufacturers provide Spice and/or Saber models. The gate drive of the source follower totem pole is much simpler at low voltage. Applications of the Complementary Totem Pole The two most common applications of the complementary totem pole are the following: - Complementary source followers as buffer drivers. Typical applications are shown in AN-937. Complementary pairs in audio amplifiers. Figure 1 Totem pole driver stage for power MOSFET If in the above example the power MOSFET was required to switch at a frequency of 1MHz and driven to 8VGS the power dissipation in each driver transistor can be calculated, worst case (assuming Rg = 0), as approximately: PD(npn) = ((VCC- VG/2) † Q † f) + (VBE † IB † t † f).

Totem Pole Mosfet Driver For Macbook Pro

| Page 35 of 47 | |||

| Author | Message | ||

| ltopower Regular Member Joined: 08/03/2019 Location: United Kingdom Posts: 64 |

'But I am still not absolutely certain in my own mind exactly HOW it works.' Glad its not just me... Another set of really interesting charts... In the original W7 modification Andrew added a 820mH choke on the output with a smaller cap as an 8kHz filter to block any connected loads feeding back changes to the resonances within the inverter. This should also help smooth out some of the distortions. High 'Crest Factor' load is shown really nicely for the Mac Book power supply... UPS units define the crest factor capability in the specifications, typically they can handle around 3. The UPS profile looks like a harmonic is causing the spikes with the spacing ? As I understand the smaller UPS units they are typically HF, which should not cause spikes like what you are seeing in the charts. Would be really interesting to see the UPS connected up with an inline LC for 8kHz in place (820mH and 0.47uF)... | ||

| poida Guru Joined: 02/02/2017 Location: Australia Posts: 998 |

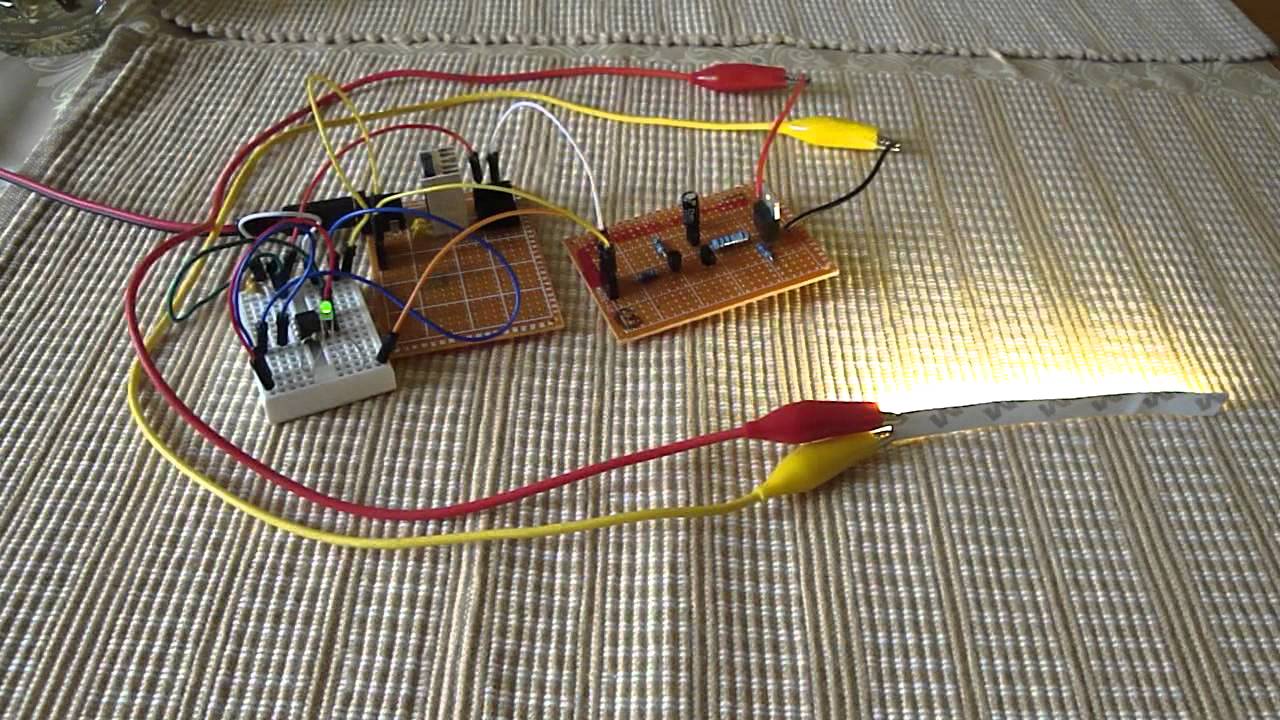

Part 30: MOSFET gate voltages with Madness's power board Now the nanoverter is running well, I have found it useful for looking at potential causes of failure with our inverters. This time I am looking at the dv/dt induced voltage changes at MOSFET gate pins and the voltages seen at the IR21844 gate drive IC outputs. I have been very wary of negative voltages appearing on the drive IC outputs. I suspect these -ve voltages have resulted in inverter failures. I have no proof, mind, but IR specify Absolute maximum rating for Vlo as from -0.3V to (Vcc+0.3V). I have seen Vlo voltages much less than -0.3V in other inverters I tested on the bench. This has lead me to use and recommend 15V TVS diodes across Vlo to ground and Vho to Vs (high side gate drive and VS). Now the Madness power board is built, let's see what voltages appear on the gate drive outputs, now they only need to drive the two transistor base pins, thanks to Madness choosing a on-board totem pole gate drive design. (yet more DSO screens follow) Light Blue is IR21844 gate drive output, sampled very close to the IC pins. Pink is MOSFET gate voltage Firstly, no load condition. Close to the beginning of a 1/2 wave: Notice the MOSFET gate exhibits large voltage spikes due to dv/dt (i.e. fast voltage changes at VS) These spikes do not find their way back to the gate drive IC outputs. Nice. Now at the other end of the 1/2 wave: Again, the negative pulse was not seen at the gate drive IC. Something else to see, there is indication of oscillation when the low side MOSFETS switch ON, to pull VS to ground. This oscillation is also not present on the gate drive IC outputs. Now, with 150W load, we see near the start: A lot more changes on the gate voltage at the MOSFET. Look at the huge negative spike just before MOSFET switch ON. That was completely insulated from the drive IC pin. None of it got through. We can see more energetic oscillations now, with a bit of load on the bridge. And near the end of the half wave, under load: pretty much the same. I have to conclude that totem-pole MOSFET drive has shown the best, least potentially destructive gate drive voltages on the IR21844 drive chips. This seems to me to be the way to go in power board design. Wiseguy has a project using potentially better performing gate drive, made with optocouplers and isolated DC supplies, etc. I look forward to seeing how his design works too. I think the inverters we have built, using the outputs from the IR2110, direct into MOSFET gates, via a 5R resistor (or something) bring some issues of reliability thanks to the dv/dt voltage pulses that can damage the gate drive ICs. My idea of using 15V TVS diodes is a bandaid. It works. But I think to avoid conveying damaging voltages back to the drive ICs would be the better approach to take by using totem pole drives located close to the MOSFETS. Totem-pole drive: This is a small clip of Tinker's schematic. The gate drive IC output is fed into the bases of the two transistors via the 22R resistor. If the current is high enough, one transistor will conduct. If the current is low enough, the other transistor will keep conducting. Both won't be conducting for very long. Voltages appearing on their emitters and collectors won't get back to their base pins, as we have seen in the above DSO traces. this is how the testing was done: Looking at the traces again, I see the gate drive IC outputs exceeding 15V, maybe getting to 16.5V. This is not good, I know the IC's have a supply of 15V. The specs say no more than DC supply + 0.3V I think we need the TVS or 15V zener diodes after all! I will put them across the point where the two transistor bases join, and to ground or VS where appropriate. | ||

| Warpspeed Guru Joined: 09/08/2007 Location: Australia Posts: 4010 |

My understanding of this negative transient on the gate driver problem, is that there are two very different integrated circuit technologies. A great many of the switching power supply control chips have outputs capable of driving large mosfet gate capacitances. These chips also have a lot of internal analog circuitry such as op amps, voltage references, and so on. Most if not all use bipolar transistors throught, including the gate driver output stage that provides the high current drive output. If you read the application notes, they specifically warn about negative voltages on the output causing catastrophic latch up, and destruction of the chip, and they often recommend connecting really enormous Shottky diodes down to ground to block these negative transients. The other type of mosfet gate driver chips you will see are all CMOS technology, and use large mosfets in the high power output stage. These chips have mostly all digital circuitry internally. Anyhow, the two large mosfets on the output have the usual drain/souce diodes that effectively clamp any transients and so the latchup problem does not exist. So it might be a really big problem with bipolar chips, or it might be no problem at all with CMOS chips. Just look up the data sheet for whatever drives your mosfet gates, and read the application notes. Then you will know for sure. All the International Rectifier IR21xx devices are CMOS so there are no worries about ringing or transients punching back into the driver with destructive negative (or positive) transients. All the dedicated high power gate driver chips like TC4452 are o/k too, as are the opto isolated gate drivers like HCPL3120. Its only the complex PWM switch mode control chips that have a lot of analog circuitry inside you need to be really careful of. | ||

| poida Guru Joined: 02/02/2017 Location: Australia Posts: 998 |

Warp, I understand that output stages can be robust and can be weak. I have no idea how robust the IR gate drive IC's output stages are. Their specs for both IR2110 and IR21844 say no less than -0.3V to ground on low side drive output, similar for high side output, w respect to VS. How much current on that negative voltage that will be tolerated is not specified. 1uA and -1V is not a lot for the body diode to deal with. I am considering various issues I need to deal with should I start to build one of your non PWM type inverters. eg. first get the transformers. Ok, looks around. Can't find no transformers... I will enjoy doing the gate signal sequencing via microcontroller, and I guess you council not to do it that way. I can't get my head around how you modulate the output voltage. I like the direct control, no PID design. But how it works, I have no idea. I suspect it's narrowing or widening the waveform, with a variable amount of zero voltage time at zero crossing. How do you do it? I figure I need to build one so as to play along with Mark when he builds his. Anyway, 15 minutes after posting Part 30 above, I applied power to Madness' power board for about the 50th time and bang. All low and high MOSFETS of one side have gone short. Only 6 dead. I rebuilt it with one MOSFET on each leg. I was hearing a small 'tick' sound when I apply power and past experience suggests that both low and high side might be conducting for a short time as things sort themselves out. I suppose things to prove might be: 1, nanoverter has gate output shutdown in effect at all times from zero DC supply, all the way to after the LCD shows data and is ready to run. 2, the totem pole drives all remain inactive at all times from zero DC, up to ready to run. I can do that, 4 channel DSO on all 4 gates. It will show if one gate or other is pulled high enough into conduction. wronger than a phone book full of wrong phone numbers | ||

| johnmc Senior Member Joined: 21/01/2011 Location: Australia Posts: 245 |

Poida, Thanks for the insight on destroying fets. (the game is called inverter Roulette) I have destroyed more than 100 fets, and it is nearly always after initial start up as you demonstrated tonight . I have not had another start blowup since, I make sure that the main power capacitors are at zero voltage (short capacitor out) then charge the capacitor by zapping 48v to the supply . then switch the inverter on. My reasoning for the above is to make sure that no residual voltage, has enabled one or more fets to remain switched on cheers johnjohnmc | ||

| mackoffgrid Guru Joined: 13/03/2017 Location: Australia Posts: 460 |

Poida, Tony will explain the operation of his inverter far better than me. But if this helps. To create the sinewave output, just think of it as a 4 bit DAC, where each bit is a ternary bit instead of a binary bit. To create a single wave he uses 1kbyte of eprom space. To modulate the output with respect to battery voltage, you change the 1kbyte address space of the eprom. In my case I'm using half of a 4Meg eprom which gives 256 discrete waveforms to choose from. Might be fun to try driving it with a micro, but the eprom method is easy and rock solid. Someone asked if batteries can be charged by back-feed from a grid-connect inverter via Tony's stepinverter; yes, it would work every bit as well as a pwm inverter, probably better since it doesn't have to fight through the pwm chop - but it hasn't been done that I know of. Cheers Andrew | ||

| Warpspeed Guru Joined: 09/08/2007 Location: Australia Posts: 4010 |

That would probably be the best way to begin. Winding the dc voltage up and down scrolls through the range of lookup tables, and you can clearly see on an oscilloscope what is happening to the steps on the output. I can supply a control board and rom, and you can then get a working inverter with that all going fairly quickly. If you make up your own microcontroller board and use the same type of plugs and connections you only then need to get the software working into known working inverter hardware. It would also eventually give other Forum members a choice of controller board. Neanderthal warp type hardware, or the Poida software driven version, as a direct plug in alternative. | ||

| noneyabussiness Guru Joined: 31/07/2017 Location: Australia Posts: 362 |

Poida, i have a few small toroidal cores you can have , around the 250watt mark, if you want... ill double check, but i have at least 3, maybe 4... just let me know and ill post em to ya..I think it works !! | ||

| poida Guru Joined: 02/02/2017 Location: Australia Posts: 998 |

I think they might be useful, what are the winding voltages? I am hoping convenient. I don't want to hand wind a 100V at 0.3V/turn. wronger than a phone book full of wrong phone numbers | ||

| Warpspeed Guru Joined: 09/08/2007 Location: Australia Posts: 4010 |

Poida, if you are not exactly thrilled by the idea of winding four transformers, there is another simpler easier way .............. When I was mucking around with all this, I invented a 'virtual inverter' to test my waveform generating control board and lookup table functionality, and voltage correction accuracy. No transformers, no mosfets, no heat sinks, and no humongous capacitors. No flames, burning smells, or smoke either. The trick is to feed the four inverter drive waveforms straight into a 256 x 256 lookup table. That is latched to eliminate all the settling time noise, then fed into a multiplying digital to analog converter. We have 81 possible output steps (mosfet gate logic states) peak to peak. If each step corresponds to 3 bits of our A/D that gives us 243 bits of analog sine wave output. It behaves just like four bridge inverters driving four output transformers. Not only that, the analog multiplying input can be tied through a voltage divider to the dc input. When the dc input rises, the amplitude coming out of the DAC rises. Exactly as the square wave amplitude from four switching bridges rise with increasing dc voltage. The whole contraption behaves exactly like four switching bridges and four transformers. It will voltage regulate and behave EXACTLY like four real inverters, with four real transformers, and you can watch the stepped output sine wave on an oscilloscope, and have fun playing software games without the fires and explosions, or spending a lot of time and money on building really serious hardware. Its not a thing of beauty, but here is my 'pretend' inverter (without a latch), and it works fine, but a latch would remove all the very fine spikes on the analog output. I used an RC filter on the output, but a latch would be far better. | ||

| ltopower Regular Member Joined: 08/03/2019 Location: United Kingdom Posts: 64 |

E70 ferrites arrived and have been trying out the odd one or two combinations... 24 actually.. Most interesting one is uH vs idle current. This is uH overall for 4 inductors, one per winding. The board was fed 50V and is coupled up to a 29V to 240V transformer, 6kVA, 25kg. This is not the whole story though, because there is some ripple left over in the output waveform, which impacts the rms value... So, for reducing idle power, there is a very clear knee point, however adding more inductance just decreases output ripple. The knee point is lower than I expected, around 25uH.... My setup is a bit convoluted as I am powering the inverter board via a 1000W boost converter via a 30V/10A power supply.... quite fortunate as I found out the hard way (without smoke, flashes and a replacement) that I can shut the unit down trying to measure the AC out by grounding one side with the scope lead... Shutdown of the unit with the large toroidal unit is no problem (at least with the small power supply !) but they have added a separate jumper onto the board at the top side of C24 (opposite pins) rather than removing the opamp.. | ||

| ltopower Regular Member Joined: 08/03/2019 Location: United Kingdom Posts: 64 |

Forgot to remove the two outliers from the second chart, I had re-tested the turns and output again... so the result is a relatively smooth series. | ||

| ltopower Regular Member Joined: 08/03/2019 Location: United Kingdom Posts: 64 |

Last chart, Idle wattage vs transformer output voltage... Not much to gain going lower than 230V... 240V in the transformer is around 1.42T. | ||

| ltopower Regular Member Joined: 08/03/2019 Location: United Kingdom Posts: 64 |

Another chart.... this one is input supply voltage vs Idle amps | ||

| ltopower Regular Member Joined: 08/03/2019 Location: United Kingdom Posts: 64 |

The Idle amps is at 30V... and about 10%-15% loss needs to be factored in (subtracted) due to the boost converter. This is the amp measurement from the 30V bench power supply unit. | ||

| noneyabussiness Guru Joined: 31/07/2017 Location: Australia Posts: 362 |

I think they might be useful, what are the winding voltages? I am hoping convenient. I don't want to hand wind a 100V at 0.3V/turn. Ill check them out as soon as i can. I have 1 bare transformer, but the others are still factory set... I think it works !! | ||

| poida Guru Joined: 02/02/2017 Location: Australia Posts: 998 |

Well done in your lucky escape thanks to the power supply. It only takes one time to learn the ground lead of a CRO is equal to house AC supply ground. The last time I learned it, again, was using a ground clip in a circuit I 'thought' was isolated but was not. What's that smell?wronger than a phone book full of wrong phone numbers | ||

| poida Guru Joined: 02/02/2017 Location: Australia Posts: 998 |

If you do it all 'live' with a microcontroller its going to be difficult to solve the time criticality problem. I doubt if you can find a microcontroller with enough internal rom to do it with just lookup tables alone. Warp, I just wrote code to do it using an Ardion Uno. 32Kb program space 16MHz clock. The main interrupt code that does all the work uses 20% of total clocks. I want to suggest that it's easy to make it work with a uC. And have it boot up and run like clockwork, in a way that does not destroy the system. Other cheap uC devices like the STM32 or the ESP32 run at far faster clock speeds and do 32 bit operations. And have huge program space. It's not a problem to use a uC.wronger than a phone book full of wrong phone numbers | ||

| Warpspeed Guru Joined: 09/08/2007 Location: Australia Posts: 4010 |

I never had the slightest doubts that you could do it. Its only easy if you know how !! Its all way beyond my skills and ability. If we all work together and help each other, truly great things can be accomplished.Cheers, Tony. | ||

| poida Guru Joined: 02/02/2017 Location: Australia Posts: 998 |

Its only easy if you know how !! Its all way beyond my skills and ability. If we all work together and help each other, truly great things can be accomplished. | ||

| Page 35 of 47 |